- 177.03 KB

- 2022-05-11 18:36:15 发布

- 1、本文档共5页,可阅读全部内容。

- 2、本文档内容版权归属内容提供方,所产生的收益全部归内容提供方所有。如果您对本文有版权争议,可选择认领,认领后既往收益都归您。

- 3、本文档由用户上传,本站不保证质量和数量令人满意,可能有诸多瑕疵,付费之前,请仔细先通过免费阅读内容等途径辨别内容交易风险。如存在严重挂羊头卖狗肉之情形,可联系本站下载客服投诉处理。

- 文档侵权举报电话:19940600175。

《嵌入式系统硬件设计》教程第九讲嵌入式体系中的基础电子线路设计编著与讲演:怯肇乾一.上述相关讲义的回顾与知识准备相关讲义的回顾:嵌入式硬件体系中的相关基础电路及其作用。知识准备:整流、滤波、监控、复位、振荡器、掉电保持、待机、电磁抑制、低功耗等;二.电源供应及其监控电路的设计1.AC-DC变换电路⑴AC-DC电源:电路组成:变压、整流、稳压、滤波。常用主要器件:DC-DC半/全桥、LM系列稳压器件等。⑵DC-AC逆变电源:常用于LCD的EL与CCEL背光电路,可用IC器件搭建,也可用成品模块。IC器件搭建背光电路,如IMP的IMP525/562/803,配合少许阻容感器件,构成EL背光电路;Maxim的Max1635配合变压器构成EL背光电路;Maxim的Max1610、Linear的1182或TI的Vcc3972与变压器件搭建CCEL背光电路。成品背光模块如森宝的VET-N1210-01CCEL模块、精电逢远的PYE系列EL/CCEL模块。用IC1

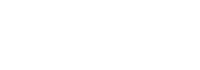

器件搭建背光电路,可以紧凑设计结构并降低成本,常常在嵌入式系统设计中采用。VinXC6203X2522.5V2.DC-DC变换电路VinVout++GND常见DC-DC变换的类型有:升压、降压、恒压、恒流、倍压、负压等。1u1u嵌入式系统中常需进行1.2V、1.5V、1.8V、2.5V、3.3V、5V等特殊器件电源供应电路设计。很多半导体厂商生产各种类型的系列微功耗高性能电源器件,如Torex的XC6203系列、Richtek的RT9168/A系列电压调整器,AME的AME8800系列、AME8811系列降压器,OnSomlconductor的NCP1400A系列、Maxim的Max1795系列升压器,等等,这些器件,提供的输出电压可是1.5~5V间的任一值,±1.2~±2.5%的精度,最大输出电流在100~500mA。选用这些器件,外配几支阻容感器件或肖基特二极管件,就可设计出适合LCD控制驱动器件的基本电源电路。右上图是2.5V电源变换电路,非常简洁。选择器件时要注意其变换效率和欧姆功率。3.系统电力监控电路通常采用专用监控IC器件对系统或其某部分电路的电压变化进行监视,一旦监测点电压低于设定值,即产生报警,引起CPU进行关键性数据存储,关掉大功耗电路模块,进行主备电源切换等。常用的电压监控IC器件:IMP的IMP811(2)、Torex的X61A(C)系列、Holtek的HT70xx系列、Ricoh的RT31xxx1系列等。一些专用复位器件里也含有类似的电压监视模块,如TI的TPS31xx系列、IMP或Maxim的705、706、708、813等。4.交流/电池供电系统的电源切换多用于便携式产品设计中,切换过程应该尽量避免用户干预、保证能量损失最少。具体设计中要避免在电池供电回路中插入串联元件,因为,当电池电压较低时,串联元件将会在电流回路中引起额外的电压降,从而降低总体转换效率。减小电池电流回路中的电阻可有效延长电池寿命。当插入墙上适配器时,任何由电池供电的DC/DC电路应从电池中吸取电流最小(最好为零);交流电源供电时,系统需防止对电池的反向充电,除非充电是被一个充电电路所控制。设计中常采用的方法:二极管隔离、MOSFET开关、有交流切换的双输出DC-DC等。三.CPU控制器的复位电路的设计复位电路设计的好坏,直接影响到整个系统工作的可靠性。很多时候,在系统设计完成并在实验室调试成功后,在现场却出现了“死机”、“程序走飞”等现象,这主要是单片机的复位电路设计不可靠引起的。2

复位电路主要有四种类型:微分型复位电路;积分型复位电路;比较器型复位电路;WatchDog型复位电路。现在的WatchDog型复位电路,多使用专用复位芯片,如Maxim的Max813等。各种复位电路中,微分复位电路简单,但易引入干扰没有监控CPU运行的能力;积分复位电路简单可靠,但由于对电源电压波动不敏感,从而有可能出现CPU由于电源电压的瞬间过低而造成工作不正常的情况;比较器复位电路电路较复杂,工作可靠;Watchdog复位电路电路较复杂,工作可靠并且具有监控CPU运行的能力。在使用中应根据电路板的空间、电源电压特性、系统运行现场等情况,综合考虑而定。设计参考:⑴在使用微分型复位电路并且使用稳压电源时,应考虑在电容输入端加入适当的电感以减少负载突变而引起的干扰复位脉冲的产生。在电路板空间有限的情况下可以选用此复位电路。⑵在使用积分型复位电路时,一方面应着重考虑上电复位时电源电压的上升率,特别在电源电压上升率较小时,应考虑用较为复杂的比较型复位电路。另一方面应考虑电路是否有降压举措以降低功耗,若有则应考虑二极管的正向压降对复位电路的影响。⑶在设计比较器型复位电路时,应着重考虑电源电压的波动性。当系统工作在恶劣环境下时,外界干扰的窜入可能引起毛刺电压,从而导致不正常的复位。为此有必要根据毛刺电压的峰峰值以及脉宽采取以下措施:(a)当毛剌电压峰峰值没有达到电源电压的正常值与系统正常工作所需最低电压值之差时,可适当降低比较器的复位电压下限;(b)当毛刺电压峰峰值超过电源电压的正常值与系统正常工作所需电压之差时,一方面应采取措施降低毛刺电压,另一方面应采用较为复杂的比较器型上电复位电路。⑷在选用或自己设计Watchdog型复位电路时,应注意输入Watchdog的“喂狗”信号应该是沿信号,而不是电平信号,同时应考虑撤销复位电压的电源电压值应大于系统最小正常电压值。四.驱动与控制器件的振荡发生电路设计1.基本的正弦振荡电路一个正弦振荡电路有四个部分组成:放大电路,正反馈网络,选频网络,稳幅电路。振荡建立的条件是:必须具有选频特性的正反馈放大器。电路稳定振荡的条件:AF=1。按选频网络组件不同,可分为RC,LC,石英晶体正弦振荡电路。RC正弦振荡器适用于频率较低的场合(1Hz~1mHz)。常用的有两种RC振荡器电路:移相式RC振荡器和桥式RC振荡器。移相式RC振3

荡器此电路适合振荡频率固定,精度要求不高的场合。桥式RC振荡器,频率可调性好,波形较好。LC正弦振荡器用于产生1mHz以上的信号,适用于几十kHz至几百mHz的频率范围(高频率和超高频),常用的LC振荡器有互感耦合(变压器耦合)LC振荡器和三点LC振荡器两种。三点式LC振荡器的电路特点是LC并联回路的三个断点分别接到管子的b、e、c三个极,称为三点式LC电路。常见的三点LC振荡器是电感三点式和电容三点式。2.石英晶体及其振荡器LC1R11⑴概述:石英晶体振荡的原理是压电效应(PiezoelectricEffect),其等效电路如右图所示。等效电路由L1(谐振电感)、C1(谐振电容)、R1(电阻)、C0(静态电容)组成。R1、C1与L1组成晶体的"谐振臂"。所有参数都可以C自定义,但要整体考虑,一个参数的变化与其它参数的变化是相联系的。0⑵基波与谐波振动(Fundamental&OvertoneResonance):石英晶体单元的频率是受振动的石英要素的物理尺度限制的。对通用的晶体单元,"AT"切片晶体单元,其厚度越小,频率增长越快。在某点,通常约30.000mHz,石英面厚度,对于加工,变得非常薄。[再去减少晶体厚度,己经不能很好地做到了。30.0mHz以下的晶体振荡频率,是"给定机械尺度的自然发生的频率",称为"基波(fundamental)"频率]。石英晶体单元能够以其"基波"频率的奇数倍数振荡。基此,可以在不去尽量减少晶体厚度的情况下,开发高于限定频率值的振荡器。即,如果一个晶体单元有10.0mHz的基频,它也可以以基波频率的3、5、7等倍数的频率构成振荡,就是说,晶体单元将以30.0mHz、50.0mHz、70.0mHz等振荡。这些基波频率倍数的频率叫做谐波(overtone)频率,用整数倍数标示,如3倍谐波、5倍谐波等。使用所需的谐波(overtone)频率时,必须指定晶体单元工作的希望操作频率和希望谐波(几倍频)。决不要定购一个基波模式的晶体单元,然后把它操作在谐波频率下。对基波和谐波晶体单元的制造加工是不同的。["基波"频率与"谐波"是怯肇乾的叫法]⑶串联/并联谐振频点及其电抗曲线:石英晶体单元有两个零相位频率。第1个,两个中较低的,感性是串联谐振频率,通常简记为fS。第2个,两个中较高的,是并联谐振频率或反谐振频率,简记为fa。fSfaf振荡电路中,串联与并联谐振频率表现为纯阻性。在串联谐振点,电阻最小,电流最大。在并联谐振容点,电阻最大,电流最小。因而,并联谐振频率fa,从来不能作为振荡电路的控制频率。石英晶体单性元可以在串联谐振点与并联谐振点之间的曲线上的任何点,由含有电抗性的元件(通常是电容),在振荡电路的反馈闭环中,组成振荡。此时,振荡频率,比串联谐振频率fS大,比并联谐振频率fa小。由于源自附加电容的频率高于串联谐振频率,该频率通常称作并联谐振频率,虽然它不是实际的并联谐振频率fa。11串联谐振频率f=,并联谐振频率f=。Sa2πLC2π(C||C)L11011⑷石英晶体振荡电路:石英晶体及其放大器等构成的振荡器,统称为晶体振荡器。4

①串联电路(SeriesCircuit):设计操作在晶体的自然串联谐振频率体。电路反馈闭环中没有电容。串联R1谐振振荡电路因其元件数量少而首先使用。然而,除了晶体外,这些电路可以提供反馈途径。因而,即使晶C1体失效,电路可以以某一振荡频率继续振荡。串联谐振振荡电路没有提供调整输出频率的手段。电路中,R1ICIC用于偏置反相器,使其工作在线性区,也给其提供负反馈;C1是耦合电容,用于隔断DC电压;R1是晶体单YR12元的限流电阻,应注意不能选择得大小;Y1是串联谐振晶体单元,它具有希望的操作频率值、频率误差和频率稳定度。"串联"电路主要用在不含电抗性元件的振荡器反馈环中。②并联电路(ParallelCircuit):所产生的晶体频率,比串联谐振频率fS高,比并联谐振频率fa低。除了晶体R单元执行反馈回路外,这些电路不提供途径。如果晶体单元失效,电路将不能继续振荡。电路的反馈回路中,使1用了一个单一的反相器和两个电容。这些电容包含"负载电容",与晶体单元一起,建立振荡器操作的频率。负载电容的值是可变的,因而振荡器的输出频率也是这样的。因此,电路提供了一个便利的调整输出频率的手段。电IC阻R1和R2的功能与串联振荡电路相同;两个负载电容C1和C2,用于建立晶体单元与振荡器的振荡频率;并联YR12谐振晶体单元Y1,与具有特定值的负载电容一起工作,它具有希望的频率值、频率误差和频率稳定度。"并联"电路主要用在含有电抗性元件(通常是电容)的振荡器反馈环中。[很多微控器的时钟电路经常采用这种形式,实际上CL1CL2是晶体两个负载电容构成了电容LC三点式振荡电路]。(怯肇乾的解释)③负载电容(LoadCapacitance):负载电容是PCB板上晶体脚间的电容数值。串联谐振振荡电路不用负频率载电容,无需考虑。并联谐振振荡电路采用有负载电容。直接测量负载电容是不现实的。通常需要计算负载变电容的值。负载电容值的计算方程式为:CL=(CL1||CL2)+CS。这里,CL1、CL2是负载电容,CS是电路的漂移化电容,CS通常取3.0~5.0pf。必须注意负载电容值的变化将引起输出频率的变化。因此,如果需要精确的频率控制,就需要精确的负载电容规范。举例来说,特定的20.0mHz的晶体单元振荡电路,使用20.0pf的负载电0ppm容;如果使用30.0pf的负载电容,实际输出频率就会变低;如果使用10.0pf负载电容,实际输出频率就会变"X"CL高。输出频率与负载电容的关系如右图所示。负载电容变化④谐波(overtone)振动应用时对振荡电路改进:很多情况下,用于特殊振荡R设计里的IC特性表明,为确保以希望的频率和奇数倍谐波工作,需要抑制晶体R11单元的基波频率。此时,常常需要修改振荡电路。有一种方法,是增加一个由C1ICICIC一个电感和一个电容组成的"储能"电路。所有图中情形,储能电路调谐共振在基Y1RR波与所希望频率之间的某一频率点上。结果,不想要的频率被避开至地,仅剩2Y2C1下所希望的频率出现在振荡器输出端。CL1C⑸晶体及其振荡器件:石英晶体(QuartzCrystal)或石英晶体谐振器(Crystal)、CLL2L石英晶体振荡器(SPXO)或时钟振荡器、温度补偿晶体振荡器(TCXO,数字式温5

度补偿晶体振荡器DTCXO)、恒温晶体振荡器(OCXO)、压控晶体振荡器(VCXO)、高频低噪声晶体振荡器。3.微控制器系统常用振荡电路的设计晶振、陶瓷谐振槽路、RC振荡器以及硅振荡器是适用于微控制器的四种时钟源。微控制器的时钟源可以分为两类:基于机械谐振器件的时钟源,如晶振、陶瓷谐振槽路;RC(电阻、电容)振荡器。右图给出了两个分立的振荡器电路,其中图a为皮尔斯振荡器配置,适用于晶振和陶瓷谐振槽路。图b为简单的分立RC振荡器。基于晶振与陶瓷谐振槽路的振荡器通常能提供非常高的初始精度和较低的温度系数。RC振荡器能够快速启动,成本也比较低,但通常在整个温度和工作电源电压范围内精度较差。硅振荡器是集成的RC振荡器,其精度要比分立RC振荡器高,多数情况下能够提供与陶瓷谐振槽路相当的精度。在特定的应用场合优化时钟源需要综合考虑以下一些因素:精度、成本、功耗以及环境需求。微控制器系统的振荡电路形式通常有标准石英晶体/陶瓷谐振器(XT)、RC振荡器器/硅振荡器、包括晶体振荡器的外接时钟源等。五.嵌入式硬件体系中的低功耗设计低功耗设计,首先是选择好即能满足系统功能要求又具有低功耗的主要IC器件,如使用1.0~3.3VIC器件;其次是配合系统软件设计相应的待机、掉电等硬件开关电路以便及时关掉系统不需要的部分或全部模块;再就是做好系统各部分电路设计,最后是合理进行PCB板的设计。PCB设计,关键的是设计好各个电源层及其区域。等等。六.EMC/EMI电路设计6

1.电源噪声的抑制3InOut电源噪声是电磁干扰(EMI)的一种,属于射频干扰(RFI),其传导噪声的频谱大1LC3致为10~30MHz,最高可达150MHz。按传播方向划分,电源噪声有两类:一类是电C1C22200p4源线引入的外界干扰,另一类是电子设备本身产生经电源线传导出去的噪声。从形0.1u0.1u8mHC4成特点划分,电源噪声又有串模干扰、共模型干扰两类,串模干扰是两电源线之间22200p5InOut(线对线)的噪声,共模干扰是两电源线对大地(线对地)的噪声。在开关电源中或电源进线端使用电源噪声滤波器PNF可以有效地抑制电源噪声。PNF是双向射频滤波器,即可滤掉交流电源线上的外来干扰,又能避免向外界发出噪声,且对串、共模干扰均有抑制作用。PNF的结构中,电感L用来抑制共模干扰,称为共模扼流圈;电容C1、C2采用0.001~0.47uF的薄膜电容器,主要用来滤除串模干扰;C3、C4为2200~4700P的陶瓷电容,跨接在输出端,分压后接地,用于抑制共模干扰。2.电源滤波普遍的做法是,对电源进入端使用简单易用的RC或LC滤波,并选用电解电容或钽电容做低频滤波;对IC器件的电源供给端使用瓷片电容做高频滤波。为改善滤波效果,又常改RC滤波为π型RC滤波,进一步改为有源RC滤波。3.铁氧体抑制元件的的选择与使用铁氧体抑制元件元件有多种材料和各种形状、尺寸,为选择适当的抑制元件,必须知道需要抑制的EMI信号的频率和强度,要求抑制的效果即插入损耗值及允许占用的空间包括内径、外径和长度等尺寸。在PCB电路板电源进口加上铁氧体抑制磁珠,可以协助退耦电容,有效地衰减高频噪声。用在电源线上的铁氧体抑制元件要选择磁导率低的材料和截面积大的元件。当偏流较大时,可将电源出线(AC的火线、DC的中线)与回线(AC的中线、DC的地线)同时穿入一个磁管,即可避免饱和,抑制共模噪声。在板卡信号线的进出口处也常常使用铁氧体抑制元件。七.设计体验:30万像素DSC双模式数码像机的基础电路设计7

1234L9S3VRc21Rc206.8uHDVddC37C2900104100uMA0211123MA0MA073117411MA0VddVddMA0MA0Y0Y0/CBARSVddL10MA122251424MA1MA1701184048S_AgndDMA1VddVddMA1MA1Y1Y1/ProgSGndDMA223502725MA2MA267119396.8uHMA2VssVddMA2MA2Y2Y2/G2xS5VMA324262826MA3MA365120388C30C333MA3VssVssMA3MA3Y3Y3/RawAVddMA4274129MA4MA4661223714104100uMA4VssMA4MA4Y4Y4/CS1AVddMA52875430MA5MA5681233644DVddMA5VddqVssMA5MA5Y5Y5/sharpAVddL11JMP1MA6291331MA6MA672124356S_Agnd2RMA6VddqMA6MA6Y6Y6/CS2AGndM2to1MA730MA7Vddq383VddqMA732MA7MA774MA7U5AY712534Y7/CS0U8AGnd7C226.8uHLMA83144933MA8MA87615C36MA8VddqVddqMA8MA8OV681OV7620AGndMA93244334MA9MA977226431047100uMA9VssqVddqMA9MA9UV0UV0/RdisAGnd1MA1020104922MA10MA1075325MA10/APVssqVddqMA10/APMA10UV1UV1/cc656S3V41635MA1142429L8L7VssqVssqA11UV2UV2/QVGADVddMCLK354712MCLK8652330CLKVssqVssqSMclkUV3UV3/EclkoDGnd6.8uH68uHMCKEb344638MCLKMCKEf84622C28CKEVssqCLKOE/CKEUV4UV4/SLVenC26C25MWE15335237MCKEbMWE8872132WENCVssqCKEWEUV5UV5/MirDioVdd104100u22u25VMRAS173716MWEMRAS8282031RASNCWESRASUV6UV6/BPClrDioGndDVddMCAS163618MRASMCAS85919C31104CASNCRASSCASUV7UV7/B8MBA194017MCAS815BANCCASCS1/RAS1VrEQRc2MDQM01420MBAMCS0801273310C32104LDQMBA0CS0/RAS0viCLKPCLK/Ox2VrSC35MDQM136C1221MCS0MDQM1901161811UDQMBA1DQM1/CAS1HSHref/VSframeVcChg0S_RST105MCS01810415MDQM0MDQM08911516C34105CCSU6LDQMDQM0/CAS0VSVsync/CsysCMgnd39MDQM1MBA781747DRAM_1M*16BUDQMMBAFodd/SRAMMIDMD02192024MclkSclkO2812S_AgndR23MD0U4CSMgndCLK24MXclkOSBBMD13DC13MD0109SclkI27410kMD1DRAM_4M*16BMD0XclkIFrExR18MD251042MD0MD1105112MA11S_RST23SclkOC23MD2MD0MD1SDE/SDSRSTAGCen/RawInitMD36GDEAD4MD1MD21031149SclkI10pMD3MD1MD2SdataPWDN27MD48MD4Q7MD25MD2MD3101MD3Sclk113R221kVTO13R19MD59Si2301DS7MD3MD49946MD5MD3MD4SDA1MMD611C118MD4MD59762454224MclkQC24MD712MD6M3VS.22uMD410MD5MD694MD5SCL63R810kSCLCHsync/BW27MHz10pMD7MD5MD6SDAMD839L4Rc111MD6MD792JMP2MD940MD86.8uH0MD613MD7MD893MD711R9V3V2to1MD9D5MD7MD8XinR102710kMD104242MD8MD99512C21MD10IN5817MD8MD9XOutMD114344MD9MD109810pMD11MgndMD9MD10MD124545MD10MD1110045VRSTMD12V3VMD10MD11RSTinR11MD134647MD11MD1210256MD13MD11MD12RSTout1MMD144848MD12MD1310446QC20MD14MD12MD13PWDNMD1549D3V50MD13MD141064710pMD15R7MD13MD14PWDN12MHz51MD14MD151104810kMD14MD15SUSpndR653MD15BMCKEfMCKEbMD15B33FD1FQ1DFT1说明:Si2301DStransform1GRF1600FC41.SDRAM选择使用U6(1M*16位)或U4(4M*16位)之一.FQ212u/330VFC1+10u/16VFC22SA1614FC3FR4FT22.电源选择:JMP1的脚1与2相连为3V,脚2与3相连为5V.ChgONS104120p/2kV1Mtransform3ctrlJ3F3V3FR1FR2FD23.SVGA/CIF模式:固定R20,21,L9,L10,变化L9为68uH;FV111.5FC5H1210kFR7FR8.22u/330Vflash-VGA模式:固定L7~L11,变化L9和L10为20omh,删除R20和R21.H2Fgnd3FLRDH3FQ430k1M42H4辉光FD35H5FR5CR02AM-8S1.5connectFLON2N3904FR6FR9FC655k27k104TitleAGAFQ3Si2301DSCIF/VGA/QVGA双模式DSC电路原理图(1)FgndSizeNumberRevisionDA4Date:19-Aug-2004SheetofFile:C:DocumentsandSettingsRongQuMyDocuments1DSC(7620+681+W78LE812)1.DDrawnBy:怯肇乾KaiZhaoQianD12348

1234DDV3VU5CV3VD3VBatteryF3V3J1107128L13VddPVdd5V6.8uH11019R10H1VssPVddIC21Xin22560U2R3FgndH2VssPVddI10pChgON310827XC61CN2202N100kH3VddIFLON44241R1131LBOH4AVddVssIVinVoutFLRD54383C20Q1MGndH5AVssVssIXout12110pC46C45C44VssI22.1MHzL14connect40S3VS5VCgnd6.8uHTestR2L2D22104104104CgndOV6815100uHIN5819U18LCDU1U10U5B3249219LCDcsLCDmode243211C3VinVoutCom0Com0CSInt2/P10AD0/P00AD0VddP22210LCDrdUSBdet342221333uGndC4Com1Com1RDT2ex/Int3/P11AD1/P01AD1VddPU132311LCDwrLBO4412330Com2Com2WRInt4/P12AD2/P02AD2VddPAIC1639-50CK100u42412LCDdata5402461Com3Com3DataInt5/P13AD3/P03AD3VddP1LCDd3VD3VINT6392671V3VD3D3VInt6/P14AD4/P04AD4VddP5817ChgON7382791CSeg0Seg0VddInt7/P15AD5/P05AD5VddPC6713FLON8372864Seg1Seg1VssInt8/P16AD6/P06AD6VssPC13C14C17C1976L15FLRD9362969IN5817Seg2Seg2Int9/P17AD7/P07AD7VssP8514LCDgndBead79L5104104104104BT1Seg3Seg3OSCOVssP9415PWoff1124LCDcs3187Bead3VSeg4Seg4OSCIA9ctrl/Rxd/P30A8/P20A8/GPio0VssP103MCKEb1325LCDrd3296Seg5Seg5LR5LC5A13ctrl/Txd/P31A9/P21A9/GPio1VssPC2211216DEAD1426LCDwr33111USBVddD5VD1Seg6Seg6Vlcd0A14ctrl/Int0/P32A10/P22A10/GPio2VssPL1121104FLon/off1527LCDdata34126104Seg7Seg7OEctrl/Int1/P33A11/P23A11/GPio3VssP134818LCDsnap1628LCDqual3510uHSeg8Seg8IRQT0/P34A12/P24A12/GPio4C1C2C5144719LCDgndBuzzer1729SVsync3652R1IN4148Seg9Seg9BZT1/P35A13/P25A13/GPio5usbVdd154620WR183037494u71044k733uSeg10Seg10BZCE/WR/P36A14/P26C3VA14/GPio6usbVssV3V45LCDd3VRD1931R2538Seg11OE/RD/P37A15/P27A15/GPio7LCDimage44C4753R12Seg12VMU743104USBun233310k18541k542Seg13LCDgndVRST34P40ALE35RD15ALEVP55R13221VddSeg14P41EA/VppRDRCV241IntXtr132WR1657DMSeg15L16P42PSen/P46WRTOER1422340DRCT1210RST1758DPSeg16BeadP43RSTCS/SnapVMO439INT1459GNDSeg17INTVPO538Cgnd4421XinIntXtr4450VssSeg18C3VVddXtalIIntXTRDML6372220Xout3951BSeg19VssXtalOV3VExtMCUDPUSBB36BeadSeg2035CgndW78LE812POV681Seg2134D3VC3vV3V33Seg22L12R24USBdetDSR4C3VSeg23326.8uHC40C8Seg24100kQ31C7LR1LR2LR3LR431C38C43R29104Seg25LPSi2302DS10u10k10k10k10k304u7104104270D3VLCDqualLCDmodeLCDsnapFLon/offSeg26GG29Seg27CgndD6LEDPWoffC8A28R30C1027Seg28Rc3100kBuzzerR26Q52N3905SDR510u104LS1LC1LS2LC2LS3LC3LS4LC4Seg29010k像质模式快门闪光灯26104104104104Seg30Q4125Seg31RSTCgndDRCTBuzzerD5VCgndSi2303DSS3VHT1621BTitleAACIF/VGA/QVGA双模式DSC电路原理图(2)SizeNumberRevisionA4Date:19-Aug-2004SheetofFile:C:DocumentsandSettingsRongQuMyDocuments1DSC(7620+681+78LE812)2.DDBDrawnBy:怯肇乾KaiZhaoQian12349

八.小结:如何为嵌入式硬件体系设计基础电子电路九.学习与思考:你做过哪些基础电子线路设计?用了什么器件?需要进一步改进吗?怯肇乾,2004-9-510